服务热线

400-801-6772

早期的TDC电路通常由印刷电路板(PCB)上的分立元件组成,通常是模拟-数字混合电路。因此,TDC电路的功耗和体积较大,电路的一致性较差。

随着超大规模集成电路技术的发展,在保持高分辨率的同时,上止点设计正朝着高集成度、低成本、低功耗的方向发展。同时,全数字集成(全数字集成)电路设计以其流程简单、设计成本低、设计难度低、流式传输成功率高等特点成为电路设计人员追求的目标。全数字TDC也是研究人员关注的问题。

1993年,报道了一种基于环形延迟门的全数字上止点设计。该设计采用1.5微米CMOS工艺,实现了13位数字转换输出。芯片面积为1.1 mm 2,分辨率为0.5 ns。然后在2003年,作者在文献[5]中报道了一种全数字模数转换器电路,该电路基于环形延迟门的全数字TDC实现。文献报道了18位全数字ADC在0.8微米的CMOS工艺中,在0.45mm的2面积上实现。

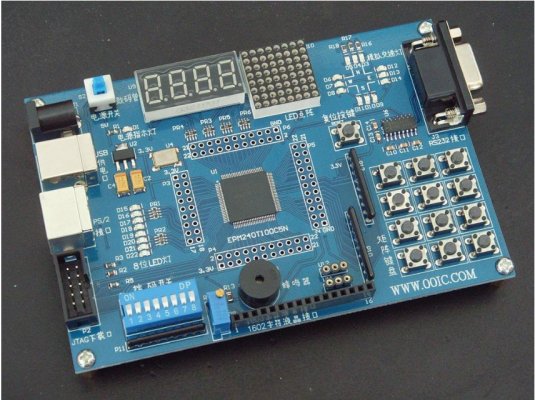

随着集成电路制造技术的不断进步,以现场可编程门阵列和复杂可编程逻辑器件为代表的PLD产业迅速发展,逐渐侵蚀了专用集成电路(ASIC)的市场份额。.这种发展使得基于PLD的TDC设计成为可能。众所周知,基于PLD的设计可以有效地缩短开发周期。

提高设计灵活性和可靠性,降低设计成本,不存在流程图风险。成功设计的IP核与过程相对独立,可以灵活移植到其他SOC,使得设计重用非常方便。

本文提出了一种基于FPGA的高精度上止点设计方法,并以环延迟门方法为参考。为了适应FPGA的设计,对延迟门方法进行了改进。如果我们简单地移植延迟门设计,它将无法在FPGA领域工作。因为与ASIC设计不同,门电路是由FPGA中的EDA软件集成的。首先,很难保证门之间延迟的一致性。第二,很难保证与其它电路的时序协调。

为了提高分辨率,与简单的计数上止点不同,也使用类似于环形延迟门设计的粗计数和细计数电路来测量给定时间。粗计数部分控制测量范围,精计数部分由环移位寄存器代替环延迟门实现。转换器在Altera系列核心上实现,Quartus II 4.2作为软件平台。仿真结果表明,该变换器的高分辨率可达3.3ns。

2。基本工作原理

基于环形延迟门的TDC系统原理框图如图1所示。PA是初始脉冲,脉冲PA的延迟信息由一个由非门组成的特殊结构的延迟链提供。在PB的上升沿,通过锁存编码电路对延时信息进行锁存和编码,脉冲PB和PA之间的时间差用输出码的数字量表示。实验结果表明,该方法适用于ASIC的实现,而不适用于FPGA的实现。

其原因是EDA工具中合成器的综合结果是基于设计对象的逻辑功能,而不是基于设计者的具体电路结构。根据FPGA电路的内部电路特点,文件[2]中提供的延迟链结构不适合在FGPA中实现。

FPGA内部路由延迟的不确定性将极大地增加各元件延迟信息的离散性。文献[6]介绍了这种方法的CPLD实现,但这种方法给特定的芯片增加了许多限制。延迟链中的每一个非门都由芯片le中的逻辑宏单元实现。由于CPLD的容量相对较小,芯片资源的利率较低,芯片之间的可移植性较差,并且由于FPGA和CPLD的结构。目前,这种差异在FPGA上还不能实现。下面是一种基于FPGA的高精度TDC设计方法。

Altera系列芯品上实现时间数字转换电路的设计

基于FPGA的TDC电路原理如图2所示。该电路包括16位环移位寄存器、16位编码器、时钟管理器、8位计数器、复位逻辑和输出逻辑。(输出逻辑)。环移位寄存器和编码器构成电路的精计数器部分,用于控制电路的测量精度;普通计数器用作粗计数器部分,用于确定电路的时间测量范围;时钟管理模块用于通过调用FPGA中的PLL资源,为移位寄存器提供合适的工作时钟;复位模块用于控制电路的测量精度。逻辑控制整个上止点电路的复位动作,输出逻辑将转换后的数字量的精计数和粗计数部分组合成终端系统的输出。

16位移位寄存器由16 D触发器组成,具有异步复位和复位终端,如图3所示。电路节点p15在初始状态或复位后处于高位,其他节点(p14-p0)